Running DRC

Running DRC

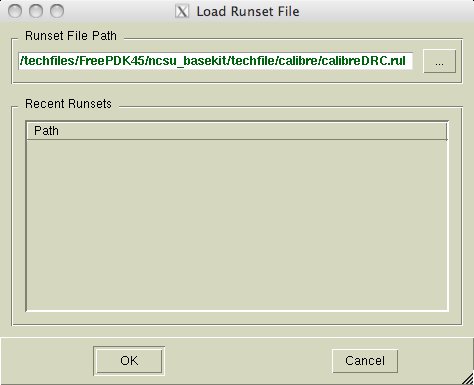

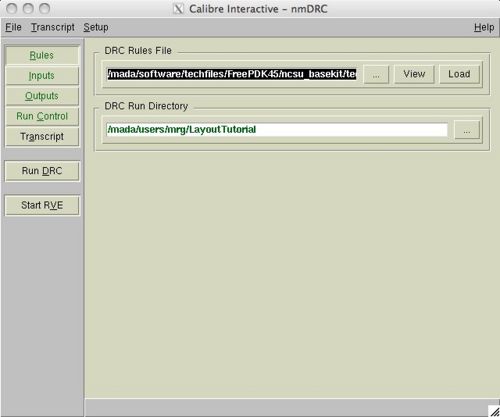

In the layout window, select Calibre->Run DRC from the top menus. This will open two new windows for DRC as shown here:

The only option you will want to change is to "Join nets with the same name". Press OK. The results are printed in the CIW. If it ends with this:

********* Summary of rule violations for cell "inv layout" ********* Total errors found: 0

then you are done! If not, you need to fix the errors.

Viewing errors

If you had errors, your summary will look something like this:

********* Summary of rule violations for cell "inv layout" *********

# errors Violated Rules

2 (SCMOS Rule 7.1) metal1 width: 0.27 um

1 (SCMOS Rule 7.2) metal1 spacing: 0.27 um

3 Total errors found

It may be obvious once you see the error where the problem is, but sometimes you need to investigate a little bit. If you go back to the layout window, some new shapes in white have been added to annotate where the errors are. Typically, these will show that two shapes are too close, too narrow, or something similar. The errors even refer to the SCMOS rule that is violated. If you don't understand, look it up on the SCMOS design rule guide.

Common errors

A common problem with DRC is when you instantiate cells. If there is not enough space from a shape inside a cell to a shape inside another cell, you will get an error. In other words, DRC is done flat. If you remove all hierarchy, you must pass DRC. Think about this when you make your cells by leaving at least 1/2 of a spacing rule between a shape and the edges of a cell. The edges of a cell are the bounding box of all shapes.