Simulation Tutorial

Contents

Select Analog Environment

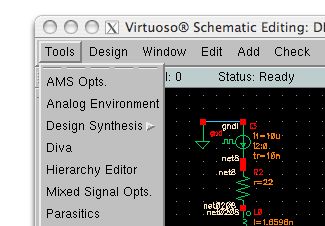

With the schematic file open, Ultrasim can be invoked from within icfb.

- Select Tools → Analog Environment.

At this stage, it is assumed that there is a schematic open with power sources and signal inputs defined. Otherwise Ultrasim is going to simulate a non powered circuit which is pointless.

This is the window that pops up once Analog Environment is chosen.

Select Simulator (UltraSim)

Virtuoso Analog Design Environment supports various simulators such is hSpice, Spectre, and Ultrasim. Ultrasim will have to be chosen before simulations can be run.

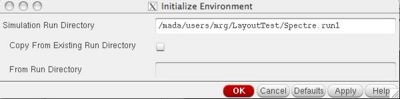

- Select Setup → Simulator/Directory/Host.

A follow up window will pop up giving your simulator options.

With current settings, hspiceD is chosen by default every time Analog Environment is launched.

- Click on the Simulator button and choose Ultrasim .

Project Library indicates where your simulation files will be stored. The generated netlist file will be stored within ~/cadence/simulation/YOUR SCHEMATIC/simulation/netlist/netlist .

*It is important to note that once the simulation has been ran, it can be initiated again via the console command

~/cadence/simulation/YOUR SCHEMATIC/simulation/netlist/RUNSIMULATION .

This way the netlist can be manually edited, saved, and simulated again without having to edit schematic and reinitiating ultrasim.

Choosing Analysis Length

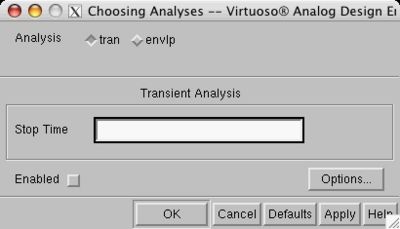

From the Analog Environment window

- Select Analysis → Choose

This will bring up a smaller window prompting you for the duration of the simulation.

Make sure tran is selected. The other option envlp is for fast envelope analysis for use on RF circuits.

Be sure to choose a stop time that is greater than the period of the input signal.

Ultrasim supports the SI prefixes so 500u would be 500 micro seconds.

Adding Model Library Files

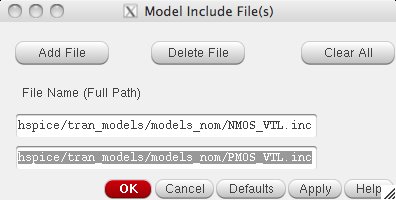

The next step is to add the spice data for the simulator.

- Select Setup → Model Libraries .

We will be adding the data for the Nmos and Pmos transistor using the TSMC 180nm process.

- Click on browse and go to: /mada/software/techfiles/NCSU_CDK_1.5.1/models/hspice/public

Make sure you click the .. first all the way till you see mada

- Select files

- /mada/software/techfiles/NCSU_CDK_1.5.1/models/hspice/public/tsmc18dN.m

- /mada/software/techfiles/NCSU_CDK_1.5.1/models/hspice/public/tsmc18dP.m

- /mada/software/techfiles/NCSU_CDK_1.5.1/models/ground.sp

Be sure to click on add after selecting each file. Select OK when finished.

Selecting Outputs to be Plotted

From the Analog Environment window

- Select Outputs → To Be Plotted → Select on Schematic

Now refer back to your schematic that is open on a different window, click on various parts to add it to the output section of the Analog Design Environment Window. (for example, the output pin Z) in your schematic that you want to be plotted. Repeat this as necessary for all nets you want to see (for example, the input pin IN).

Running Simulation and Ouput Window

- Select Simulation → Netlist and Run

This will generate the netlist file, run the simulation, and feed the results to the waveform viewer.

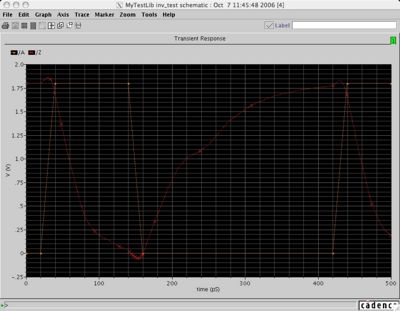

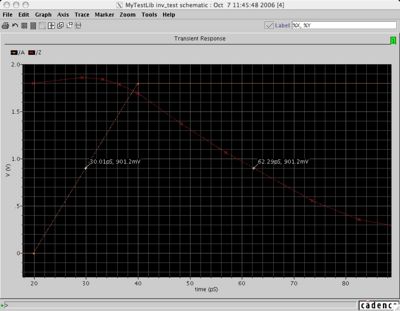

Waveform - Zooming and Trace

With the waveform window open, you can zoom in and find exact values.

Zoom

- Select Zoom → X Zoom .

- Now click and drag in the waveform window to select the x-range you want to zoom to.

Tracing

- Select Marker → Place → Trace Marker

- Click on one of the waveforms in the window. This places a small label on the waveform. You can drag this marker anywhere on the waveform.

Power Analysis with UltraSim

To enable power analysis in Ultrasim

- 1) go to Simulation->Options->Analog

- 2) In the "Advanced Checks" section, check the button near "Power analysis" and click on Setting

- 3) In the window that opens up

- 3.1) Enter * for the "subckt name"

- 3.2) Select max in the "Output Sorting" section

- 3.3) Click on Add at the top

- 3.4) Click OK to close the window

- 4) Click OK to close the "Simulator Options" window

- 5) Simulate as usual (Simualte->Netlist and Run)

- 6) Look for a file called "input.pa", most likely under /cse/grads/USERNAME/cadence/simulation/comb_adder/UltraSim/schematic/psf/input.pa

- The file will list Max,Avg and RMS power for each pin in your design, and will look something like this:

-

- UltraSim version 6.1.0.151 32bit 06/01/2006 18:35 (usimlx109)

- Virtuoso (R) Ultrasim Full-chip Simulator

- Copyright(C) 2001-2004, Cadence Design Systems, Inc.

- USER: yaron HOST: mosis4.cse.ucsc.edu HOSTID: 7280EF31 PID: 887

- Memory: available: 322.0357 MB physical: 8.3663 GB

- CPU(1 of 4): CPU0 Dual-Core AMD Opteron(tm) Processor 2218 2613.468MHz

- Netlist file: input.ckt

- Starting time: Wed Nov 28 20:32:53 2007

- .TITLE 'This file is :../psf//input.pa'

- Time: from 0n to 2000n

- *** Port Current Summary *************

- Max(A) Avg(A) RMS(A) Peak Time(ns)

- U1_3.0 3.934e-04 -2.748e-06 2.463e-05 647.008

- U1_10.0 3.935e-04 -2.626e-06 2.443e-05 587.008

- U1_15.0 3.935e-04 -2.304e-06 2.428e-05 131.008

- U1_12.0 3.934e-04 -2.566e-06 2.419e-05 1607.01

- U1_7.0 3.933e-04 -2.667e-06 2.397e-05 1511.01

- U1_4.0 3.934e-04 -2.627e-06 2.390e-05 479.008

- U1_6.0 3.935e-04 -2.498e-06 2.385e-05 1055.01

- U1_5.0 3.935e-04 -2.562e-06 2.385e-05 851.008

- U1_11.0 3.934e-04 -2.451e-06 2.383e-05 623.008

- U1_8.0 3.934e-04 -2.705e-06 2.378e-05 1943.01

- U1_9.0 3.934e-04 -2.651e-06 2.373e-05 83.0078

- U1_13.0 3.933e-04 -2.674e-06 2.363e-05 1079.01

- U1_14.0 3.933e-04 -2.585e-06 2.325e-05 275.008

- U1_1.0 3.928e-04 -2.333e-06 2.322e-05 1379.01

- U1_0.0 3.694e-04 -2.060e-06 2.266e-05 1223.01

- U1_2.0 3.934e-04 -2.481e-06 2.256e-05 1127.01

- U1_3.B 4.652e-04 -2.657e-08 1.829e-05 1681.02

- U1_8.A 4.617e-04 -7.634e-09 1.807e-05 625.016

- U1_10.B 4.651e-04 -2.194e-08 1.773e-05 1309.02

- U1_3.vdd! 4.409e-04 2.764e-06 1.770e-05 911.02

- U1_1.A 4.618e-04 -5.062e-09 1.754e-05 289.017

- U1_15.B 4.651e-04 -3.659e-08 1.753e-05 1729.02

- U1_6.A 4.618e-04 -2.262e-08 1.740e-05 157.017

- U1_10.vdd! 4.405e-04 2.682e-06 1.730e-05 1883.02

- U1_13.B 4.651e-04 -3.209e-08 1.730e-05 1465.02

- U1_3.A 4.618e-04 -2.545e-08 1.722e-05 409.017

- U1_7.vdd! 4.403e-04 2.704e-06 1.719e-05 107.02

- U1_7.B 4.650e-04 -3.310e-08 1.717e-05 1729.02