SRAM 10T

Tom Golubev's F09 CMPE222 Project

Tom Golubev

CMPE 222 F09

10/12/09

VLSI Project Proposal

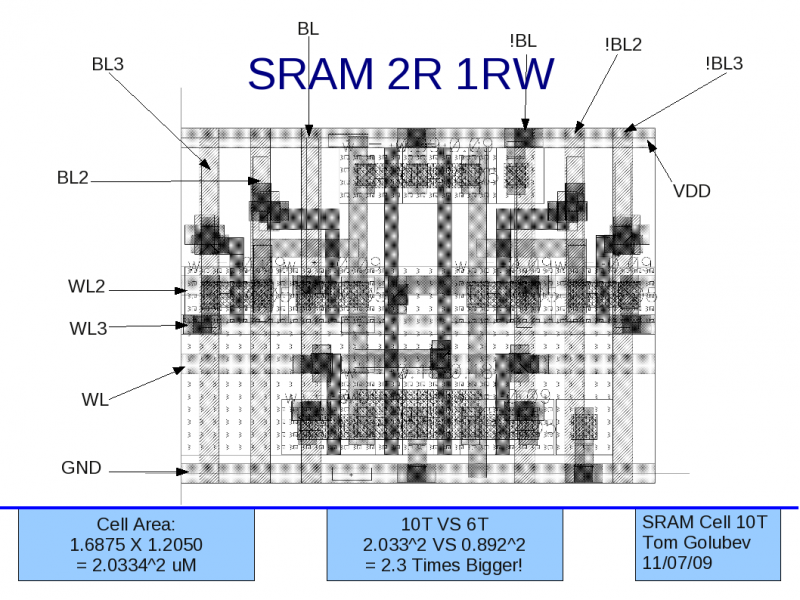

Extend the SRAM compiler to support 2 Read ports. This entails creating a 2 read port cell, making the compiler tile it, then adding more address decoders and sense amps. A high metal layer may be necessary (M3) for the decoders of the 2nd port. This project is half layout, half python compiler scripting.

* Denotes perceived difficulty, from low * to high ***

Basic Plan:

•.*Understand Python script / study 1R/1W cell

•.**Create / Simulate 2R/1W standard cell

•.*Add 2R/1W option into compiler

•.*Make compiler tile the 2R/1W cell

•.*Figure out where to put address decoders / sense amps

•.***Decide which metal layer 2nd read port interconnects will be on, metal3?

•.***Have compiler wire interconnects for 2nd port

•.**Test / Debug / validate

Extended Plan:

•.*Simulate with CACTI

•.**Try reducing area / power