Running LVS

To run LVS, you must have a schematic and a DRC clean layout.

LVS Options

There are several options when running LVS. If you go to NCSU->Modify LVS Rules, you will get this menu:

Some parameters you may want to change:

If you don't have an ntap or ptap, you can add "Ignore FET body terminal".

To force matching of sizes (a good idea), select "Compare FET parameters".

Extract a schematic

In your layout, first perform extraction by selecting Verify->Extract. Select "Join nets with same name." This command will analyze all the electrical connectivity of the different layers and create an "extracted" schematic view. This is what is compared to your schematic.

Running LVS

To open the LVS window, select Verify->LVS... In this window, you will need to select both your schematic and the recently generated extracted schematic. You can do this by browsing and selecting the appropriate cell views.

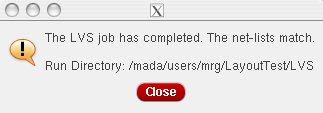

After you run it, Virtuoso will return with a message that it has "successfully completed." This does not mean it passed, it means that it RAN! If it also displays "The net-lists match." like this:

If it doesn't, you must check the log by clicking the "Output" button.

Debugging errors

There is a separate wiki page, Debugging LVS, on suggestions for debugging errors. This is a very difficult problem sometimes, but it is usually a simple swap of nets or pins.