Back Annotation

The above simulation did not actually include the parasitic capacitances and resistances of the interconnect. Spectre (or hSpice) will by default use the gate area (L and W) to estimate the gate capacitance. If there are perimeters (ps, pd) and areas (as, ad) of the source and drain like this:

m0 (Z A vdd vdd) tsmc18dP w=2.7e-07 l=1.8e-07 as=1.539e-13 \

ad=1.539e-13 ps=1.35e-06 pd=1.35e-06 m=1 region=sat

it will include those capacitances. However, it does not include any extra routing, contacts, diffusion, etc. In order to include these, you need to perform extraction and back-annotation. The extraction is similar to the device extraction you used to extract a netlist for LVS, but now it extracts parasitic devices too.

Easier Method

In order to include the extra interconnect parasitics, we must have done DRC, Extract, and LVS. There can be absolutely no errors or warnings in LVS. For example, even this doesn't allow back-annotation:

termbad.out: ? Terminal A's type in the schematic: input, in the layout: inputOutput

You should see this at the bottom of your LVS report if you have no errors or warnings:

Probe files from /mada/users/mrg/LayoutTest/LVS/schematic devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out: Probe files from /mada/users/mrg/LayoutTest/LVS/layout devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out:

Now, you are ready to back-annotate. However, in order to include the extra interconnect parasitics, we must re-extract our layout, but with an additional flags enabled. When you select Verify->Extract in the layout window, click the "Set Switches" button. This will open an additional window with a set of options. Highlight the "Extract_parasitic_caps" option. This will put parasitic resistors and capacitors in the new extracted view.

After re-running LVS, in the LVS window, press the button "Build Analog". If there was an LVS problem, it will just say "There was an LVS error." If there wasn't, this will open a second window. Just press ok to "Include All". This will create a new cell view called "analog_extracted". You can open this new view and it will look like a mash-up of your schematic and layout. This matched the parasitics from your layout with your schematic. It is pretty hard to see details in a big layout though.

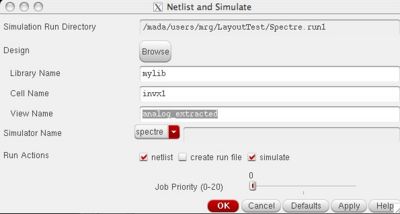

Then, to simulate the back-annotated view, you simply go to your Schematic and set up your Spectre simulation as normal. (In fact, you can just load the saved setup from the spectre.run1 directory.) Confirm that it works for the schematic. Then, go to Spectre->Netlist and Simulate, but instead of the view being "schematic", you make it "analog_extracted" and run it again like this:

Now it should have parasitics too!

To confirm this, look in your run directory (e.g. spectre.run1) and view the "netlist" file in the unix shell (or go to Spectre->Stimulus->Edit Netlist File) and you should see a bunch of transistors and capacitors. The inputs should be named normally, but other internal nets may not. Here is an example from my inverter:

// Library name: mylib

// Cell name: invx1

// View name: analog_extracted

\+1 (Z A vdd! vdd!) tsmc18dP w=2.7e-07 l=1.8e-07 as=1.539e-13 ad=1.539e-13 \

ps=1.35e-06 pd=1.35e-06 m=1 region=sat

\+5 (A 0) capacitor c=2.27853e-17 m=1

\+4 (Z 0) capacitor c=2.87838e-17 m=1

\+3 (vdd! 0) capacitor c=1.29997e-16 m=1

\+2 (vdd! Z) capacitor c=2.87838e-17 m=1

\+0 (Z A 0 0) tsmc18dN w=2.7e-07 l=1.8e-07 as=1.539e-13 ad=1.539e-13 \

ps=1.35e-06 pd=1.35e-06 m=1 region=sat

If you do not see the capacitors, then something is wrong.