Back Annotation

The above simulation did not actually include the parasitic capacitances and resistances of the interconnect. Spectre (or hSpice) will by default use the gate area (L and W) to estimate the gate capacitance, but additional poly is not considered. If you specified perimeters (ps, pd) and areas (as, ad) in the pcell form, it will include those estimates in simulation. However, it does not include any extra routing, contacts, diffusion, etc. In order to include these, you need to perform parasitic extraction and back-annotation. The extraction is similar to the device extraction you used to extract a netlist for LVS, but now it extracts parasitic resistances and capacitances too.

Your design must pass DRC and LVS to do this.

SCMOS Method

In order to include the extra interconnect parasitics, we must have done DRC, Extract, and LVS. There can be absolutely no errors or warnings in LVS. For example, even this doesn't allow back-annotation:

termbad.out: ? Terminal A's type in the schematic: input, in the layout: inputOutput

You should see this at the bottom of your LVS report if you have no errors or warnings:

Probe files from /mada/users/mrg/LayoutTest/LVS/schematic devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out: Probe files from /mada/users/mrg/LayoutTest/LVS/layout devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out:

Now, you are ready to back-annotate. However, in order to include the extra interconnect parasitics, we must re-extract our layout, but with an additional flags enabled. When you select Verify->Extract in the layout window, click the "Set Switches" button. This will open an additional window with a set of options. Highlight the "Extract_parasitic_caps" option. This will put parasitic resistors and capacitors in the new extracted view.

After re-running LVS, in the LVS window, press the button "Build Analog". If there was an LVS problem, it will just say "There was an LVS error." If there wasn't, this will open a second window. Just press ok to "Include All". This will create a new cell view called "analog_extracted". You can open this new view and it will look like a mash-up of your schematic and layout. This matched the parasitics from your layout with your schematic. It is pretty hard to see details in a big layout though.

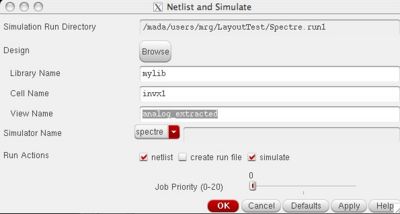

Then, to simulate the back-annotated view, you simply go to your Schematic and set up your Hspice simulation as normal. (In fact, you can just load the saved setup from the Hspice run directory.) Confirm that it works for the schematic. Then, go to Hspice->Netlist and Simulate, but instead of the view being "schematic", you make it "analog_extracted" and run it again like this:

Now it should have parasitics too!

To confirm this, look in your run directory after you run a back-annotated simulation and view the "netlist" file in the unix shell and you should see a bunch of transistors and capacitors. The inputs should be named normally, but other internal nets may not. Here is an example from my inverter:

// Library name: mylib

// Cell name: invx1

// View name: analog_extracted

\+1 (Z A vdd! vdd!) tsmc18dP w=2.7e-07 l=1.8e-07 as=1.539e-13 ad=1.539e-13 \

ps=1.35e-06 pd=1.35e-06 m=1 region=sat

\+5 (A 0) capacitor c=2.27853e-17 m=1

\+4 (Z 0) capacitor c=2.87838e-17 m=1

\+3 (vdd! 0) capacitor c=1.29997e-16 m=1

\+2 (vdd! Z) capacitor c=2.87838e-17 m=1

\+0 (Z A 0 0) tsmc18dN w=2.7e-07 l=1.8e-07 as=1.539e-13 ad=1.539e-13 \

ps=1.35e-06 pd=1.35e-06 m=1 region=sat

If you do not see the capacitors, then something is wrong.

FreePDK45 Method

This is very similar to LVS. Go to Calibre->Run PEX. You will need to specify a layer map like LVS again. Also, select the rule file as this:

/mada/software/techfiles/FreePDK45/ncsu_basekit/techfile/calibre/calibrexRC.rul

Under the Input section, in the Layout tab, make sure that GDSII and "Export from layout viewer" are selected. Under the Netlist tab, make sure that SPICE and "Export from schematic viewer" are selected.

Under the Output section, most options should be left as default. Under Netlist, we want Hspice format and names from the SCHEMATIC. By default, "All Nets" under the Nets tab should be checked. Under the Report tab, select "Generate PEX report" and "View report after PEX finishes". Under SVDB, make sure that "Start RVE after PEX" is checked.

One common error is that the pins are connected to the text layer and not the metal1 layer. You can't pass PEX unless all pins are set to metal1. Highlight the pin and press Q to see which layer the pin is connected to.

After this, there are a few files that were created, namely .netlist, .pex, and .pxi

The .pex, containing the parasitic elements for each subcircuit looks something like:

* File: invx1.pex.netlist.pex * Created: Thu Oct 1 14:51:55 2009 * Program "Calibre xRC" * Version "v2008.3_16.12" * .subckt PM_SIMPLE_INV%Z 1 2 5 8 c19 8 0 0.00519381f c20 5 0 0.0126473f c21 1 0 0.0438069f r22 8 9 102.4 r23 3 8 0.0146822 r24 3 5 0.866071 r25 2 9 1.98769 r26 1 9 2.95231 .ends

The actual netlist ("invx1.pex.netlist") with only the transistors is the .netlist file and looks like:

* File: invx1.pex.netlist * Created: Thu Oct 1 14:51:55 2009 * Program "Calibre xRC" * Version "v2008.3_16.12" *

.include "simple_inv.pex.netlist.pex" .subckt simple_inv Z A GND! VDD! * * VDD! VDD! * GND! GND! * A A * Z Z MM0@2 N_Z_MM0@2_d N_A_MM0@2_g N_GND!_MM0@2_s N_GND!_MM0@2_b NMOS_VTG L=5e-08 + W=1.8e-07 AD=2.52e-14 AS=1.89e-14 PD=6.4e-07 PS=5.7e-07 MM0 N_Z_MM0@2_d N_A_MM0_g N_GND!_MM0_s N_GND!_MM0@2_b NMOS_VTG L=5e-08 W=1.8e-07 + AD=2.52e-14 AS=1.89e-14 PD=6.4e-07 PS=5.7e-07 MM2@2 N_Z_MM2@2_d N_A_MM2@2_g N_VDD!_MM2@2_s N_VDD!_MM2@2_b PMOS_VTG L=5e-08 + W=3.6e-07 AD=5.04e-14 AS=3.78e-14 PD=1e-06 PS=9.3e-07 MM2 N_Z_MM2@2_d N_A_MM2_g N_VDD!_MM2_s N_VDD!_MM2@2_b PMOS_VTG L=5e-08 W=3.6e-07 + AD=5.04e-14 AS=3.78e-14 PD=1e-06 PS=9.3e-07 * .include "simple_inv.pex.netlist.SIMPLE_INV.pxi" * .ends

The .pxi file ("invx1.pex.netlist.INVX1.pxi") contains the connections between the parasitics and the transistors. It looks like this:

* File: invx1.pex.netlist.INVX1.pxi * Created: Thu Oct 1 14:51:55 2009 x_PM_SIMPLE_INV%Z N_Z_MM0@2_d N_Z_MM2@2_d Z N_Z_c_2_p PM_SIMPLE_INV%Z x_PM_SIMPLE_INV%A N_A_MM0@2_g N_A_MM2@2_g N_A_c_22_n N_A_c_28_p N_A_MM0_g + N_A_MM2_g A N_A_c_26_n PM_SIMPLE_INV%A x_PM_SIMPLE_INV%GND! N_GND!_MM0@2_s N_GND!_MM0_s N_GND!_MM0@2_b N_GND!_c_44_n + GND! PM_SIMPLE_INV%GND! x_PM_SIMPLE_INV%VDD! N_VDD!_MM2@2_s N_VDD!_MM2_s N_VDD!_MM2@2_b N_VDD!_c_57_n + VDD! PM_SIMPLE_INV%VDD! cc_1 N_Z_MM0@2_d N_A_MM0@2_g 0.0107699f cc_2 N_Z_c_2_p N_A_MM0@2_g 0.0014234f cc_3 N_Z_MM0@2_d N_A_c_22_n 0.00106391f cc_4 N_Z_MM0@2_d N_A_MM0_g 0.0122772f

If the above simulation gets too slow, you can run without resistive parasitics but with less accuracy. To do this, change the extraction type to "C+CC" instead of "R+C+CC".

Now, you are ready to run a back-annotated simulation.

Back-Annotated Simulation

To run simulations, copy the .pex, .pxi and .netlist file to your prior Hspice simulation directory.

Open the file named input.ckt . Delete ONLY the lines starting with M (lines containing transistors) From the PEX netlist file (invx1.pex.netlist) copy the lines starting from .include all the way to .ends (both lines included). Paste into input.ckt, in the empty space you have obtained by the earlier deletion. Comment out the .subckt and .ends lines. Save the input.ckt file and in the Analog Design Environment window, click Simulation->Netlist and Run

The middle of your input.ckt file should resemble something like this:

.INCLUDE "/mada/software/techfiles/FreePDK45-1.4/ncsu_basekit/models/hspice/tran_models/models_nom/PMOS_VTG.inc" .INCLUDE "/mada/software/techfiles/FreePDK45-1.4/ncsu_basekit/models/hspice/tran_models/models_nom/NMOS_VTG.inc" .include "invx1.pex.netlist.pex" * subckt invx1 Z A GND! VDD! * * GND! GND! * VDD! VDD! * Z Z * A A MM0 ( N_Z_MM0_d N_A_MM0_g N_GND!_MM0_s N_GND!_MM0_b ) NMOS_VTL l=5e-08 w=9e-08 \ ad=9.45e-15 as=9.45e-15 pd=3.9e-07 ps=3.9e-07 MM1 ( N_Z_MM1_d N_A_MM1_g N_VDD!_MM1_s N_VDD!_MM1_b ) PMOS_VTL l=5e-08 \ w=1.8e-07 ad=1.89e-14 as=1.89e-14 pd=5.7e-07 ps=5.7e-07 * include "invx1.pex.netlist.INVX1.pxi" * * ends INVX1 * * .include "/mada/users/rsankara/hspice_simul/simple_inv/hspiceD/schematic/netlist/stimuli/stimulus.sp" .END

Make sure, your input.ckt already has .include for the models, and .END at the end of the file

Everything else should be the same as before back-annotation! Now when you run your simulation and go to the waveform tool, you will see many extra nets due to the parasitic R's and C's like this: