Ce

Contents

== Compute Engine Design Specifications ==

ASIC AREA Estimate(dc_shell):

FPGA LUT Estimate(synplify_pro): 35,500 LUTs

The COMPUTE ENGINE of SCOORE is responsible for all the calculations of the processor. SCOORE is a clustered architecture, we have FOUR main units which comprise the COMPUTE ENGINE.

- AUNIT is responsible for all the "simple arithmetic operations" ie. add,sub,shift,AND, XOR... of the CPU.(Single Port)

- BUNIT is responsible for branch operations ie. BNE, BGE.... (Dual Port)

- CUNIT handles all floating point operations. (Single Port)

- MUNIT handles all Load and Store operations. (Dual Port)

A more detailed description of each individual block is given below.

|

|

|

Individual Unit Descriptions

Each of the four clusters in the CE holds 128 registers in its Register File. There are a total of 512 registers. A 9-bit binary number is assigned to each register. Since there are only 512 registers, the highest 2-bits are indicative of the CE cluster/unit to which they belong.

| Register Number | Highest 2 bits | Compute Engine (CE) |

|---|---|---|

| 0 - 127 | 00 | A Unit RF |

| 128 - 255 | 01 | B Unit RF |

| 256 - 383 | 10 | C Unit RF |

| 384 - 511 | 11 | M Unit RF |

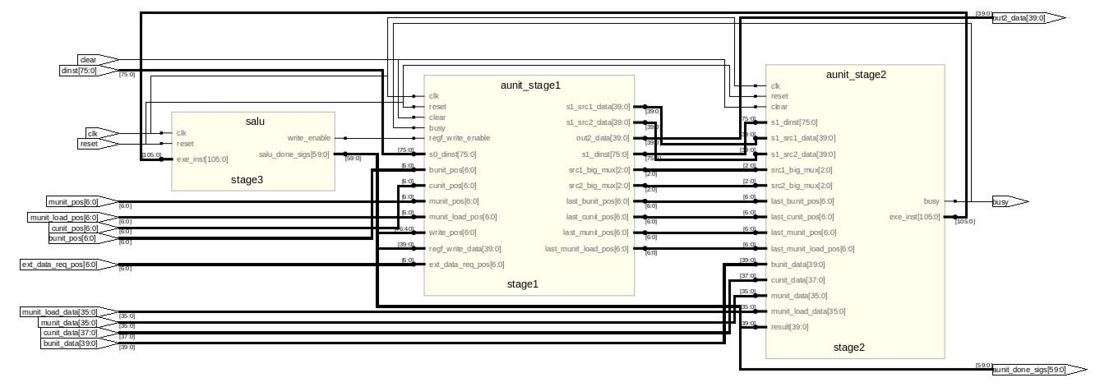

AUNIT

aunit_stage1

-Local/Ext/Imm Src Sel. Logic -Reset/Busy Logic |

aunit_stage2

-Reservation Station Logic -Forwarding Logic -Update Logic |

salu

-Single Cycle Execution Stage |

write_back

Reg. File |

|---|

The AUNIT executes the following SPARC V8 instructions:

The AUNIT executes the following SPARC V8 instructions:

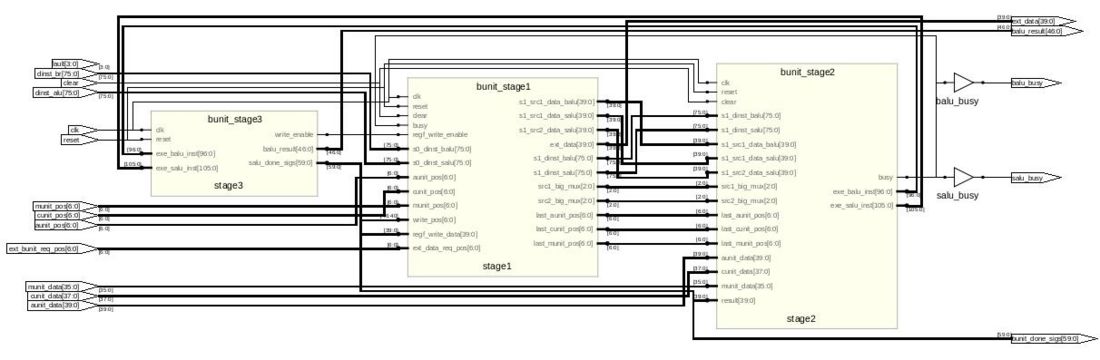

BUNIT

bunit_stage1

-Local/Ext/Imm Src Sel. Logic -Reset/Busy Logic |

bunit_stage2

-Reservation Station Logic -Forwarding Logic -Update Logic |

balu/salu

-Single Cycle Execution Stage |

write_back

Reg. File |

|---|

The BUNIT executes the following SPARC V8 instructions:

The BUNIT executes the following SPARC V8 instructions:

CUNIT

cunit_stage1

-Local/Ext/Imm Src Sel. Logic -Reset/Busy Logic |

cunit_stage2

-Reservation Station Logic -Forwarding Logic -Update Logic |

FPU

-Multiple Cycle Execution Stage |

write_back

Reg. File |

|---|

The CUNIT executes the following SPARC V8 instructions:

MUNIT

munit_stage1

-Local/Ext/Imm Src Sel. Logic -Reset/Busy Logic |

munit_stage2

-Reservation Station Logic -Forwarding Logic -Update Logic |

CACHE

-Multiple Cycle Execution Stage |

write_back

Reg. File |

|---|

The MUNIT executes the following SPARC V8 instructions:

--Rigo Dicochea 09:47, 30 March 2009 (PDT)