SCOORE

From Vlsiwiki

Contents

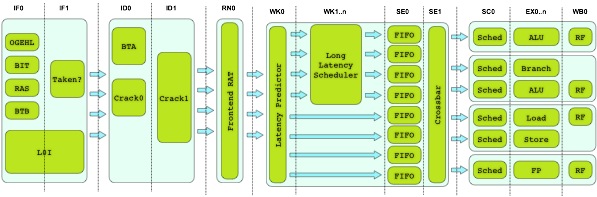

[hide]SCOORE Pipeline

Major SCOORE blocks:

- bpred: Branch predictor with BTB, OGEHL, RAS, BIT, and instruction predecode

- L0I: Instruction cache

- crack: Instruction decode/crack creates uOPs from SPARC V8.

- ratrob: Rename and Reorder buffer

- scheduler: Long latency instruction scheduler window.

- select: Instruction select stage to enforce structural hazards

- ce: Compute Engine

- L0D: Speculative L0 data cache

- L1: L1 cache

SCOORE Synthesis

SCOORE targets ASIC and FPGA. To simplify configurations the synos script automatically generates configuration files for all the tools.

SCOORE Coding Style

SCOORE uses a subset of System Verilog. The subset is selected to maximize reuse while still working in all the synthesis tools.

FPGA Boot

SCOORE has a dual ASIC/FPGA target. We target many FPGAs as long as they are big enough. This document explains how to bring up a SCOORE board.

Term Definitions

This section explains the main names that we use in SCOORE. This is a convention/agreement so that everybody uses the same language.

In addition, RAMP shares many goals with the SCOORE project. This link explains some of the SCOORE constructs from a RAMP perspective.